## **BCD Process Enables 50 Percent Power Die Size Reduction**

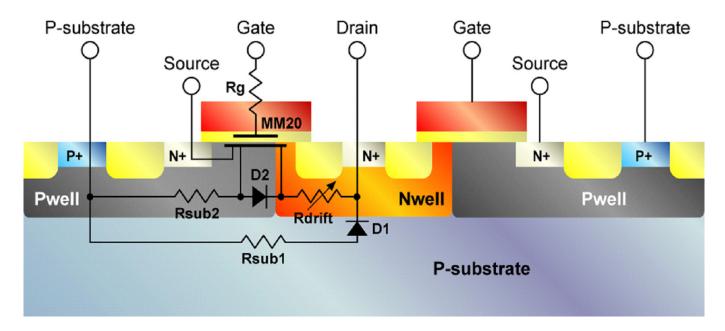

Jazz Semiconductor has developed enhancements to its advanced Bipolar CMOS DMOS (BCD) process platform including the addition of an ultra low  $R_{\rm ds(on)}$  scalable NLDMOS device enables up to a 50 percent shrink in die size in most power devices. The 0.18  $\mu$ m BCD process adds the combination of high density 1.8-V digital CMOS with the higher voltage drivers required for highly integrated Power SOC designs. The high-voltage BCD process is available in scales from 0.5 $\mu$  to 0.18 $\mu$  with features includeing VIA stacking, thick top power metal (3  $\mu$ m) for improved current-carrying capacity, ESD protection circuits, and triple well isolation.

Jazz Semiconductor 949-435-8181 <a href="https://www.jazzsemi.com">www.jazzsemi.com</a> [1]

## Source URL (retrieved on 07/28/2014 - 11:09pm):

http://www.ecnmag.com/product-releases/2008/03/bcd-process-enables-50-percent-power-die-size-reduction?qt-most\_popular=0

## Links:

[1] http://www.jazzsemi.com/

Page 1 of 1